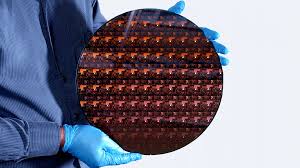

The race toward 2 nm process technology is intensifying, led by TSMC, Samsung, and Intel, powering next-generation AI, cloud, and mobile platforms while shaping global competitiveness. From the 10 µm transistors of the 1970s to today’s 20–50 nm advanced packaging features (interconnects, bumps, redistribution layers), each innovation has enabled higher bandwidth, better power delivery, and faster system-level integration.

- The historical evolution from 10 µm to nanometer-scale nodes highlights how relentless scaling created the massive economic and technological ecosystem we see today. Leadership in process technology continues to drive pricing power, customer stick-in, and global strategic influence.

- Chips integrate advanced packaging features, such as interconnects, bumps, and redistribution layers, typically in the 20–50 nm range, enabling higher bandwidth, improved power delivery, and faster system-level integration. At the same time, the most advanced transistor logic powers these systems at 5 nm today, with 3 nm nodes entering production, driving density, efficiency, and AI-ready performance.

- Shrinking transistor nodes and packaging innovations together deliver significant performance-per-watt improvements, making advanced nodes economically compelling for AI accelerators, cloud infrastructure, and mobile platforms facing rising energy and cooling costs. These efficiency gains improve total cost of ownership and long-term return on capital.

- Economics at the leading edge are increasingly shaped by yield management, cycle time, and integration capabilities, not just wafer cost. Chipmakers are turning to chiplet-based architectures to balance performance ambitions with capital discipline.

- Process advances alone are no longer sufficient, driving adoption of FinFET, Gate-All-Around (GAA), nanosheet, and FlipFET (CFET) architectures to manage leakage, variability, and reliability at extreme densities. This shift elevates demand for cross-disciplinary engineering and manufacturing expertise.

- China’s exploration of FlipFET/CFET architectures, which vertically stack n-type and p-type transistors, highlights a strategic push to increase density without relying solely on lithography. Post-2 nm competitiveness increasingly depends on architecture and integration breakthroughs.

- As chips disaggregate into multiple dies, advanced packaging has become a core differentiation and profit engine. Leading solutions include CoWoS (chip-on-wafer-on-substrate for HBM), InFO (fan-out wafer-level packaging for thin mobile chips), Foveros (3D stacking of multiple dies), EMIB (embedded bridge connecting chiplets), FOWLP (fan-out wafer-level packages for IoT/RF devices), and 2.5D interposers (substrates linking multiple dies). These solutions enable faster time-to-market while controlling cost and scaling risk.

- Control over advanced packaging capacity increasingly determines who can scale AI systems, as HBM integration, thermal management, and substrate availability become bottlenecks. Companies mastering both front-end logic and back-end integration ecosystems gain significant bargaining power.

- The 2 nm race is led by TSMC, Samsung, and Intel, each leveraging different strategies: TSMC as the manufacturing front-runner, Samsung pushing early GAA adoption, and Intel aiming for a competitive rebound with its 20A/18A roadmap. Leadership at 2 nm signals future pricing power, customer stickiness, and long-term capital efficiency.

- Expansion of 2 nm logic and advanced packaging will significantly impact employment across Asia-Pacific, increasing demand for packaging engineers, process specialists, equipment experts, and senior semiconductor leaders. Regions aligning workforce development with advanced manufacturing scale will capture outsized economic value in the next semiconductor cycle.

Facing advanced semiconductor packaging constraints or difficulty hiring senior executives and skilled engineers fast enough to scale?

We deliver high-quality carrier tapes, cover tapes, reels, and thermoforming trays tailored for the industry’s most in-demand and advanced packages – from PDIP, SOIC, and QFNs to WLCSP, chiplets, modules, and panels (for context: PDIP/SOIC – common IC packages, WLCSP – wafer-level chip-scale packages for mobile devices, chiplets/modules – integrated multi-chip solutions).

At the same time, we connect you with the best-fit Senior Management leaders, Professionals, and Technical Staff to strengthen your organisation.

For enquiries or more information, please visit https://tmbsconsulting.com or contact Richard Chuck Olivas via WhatsApp: https://wa.me/6583393490