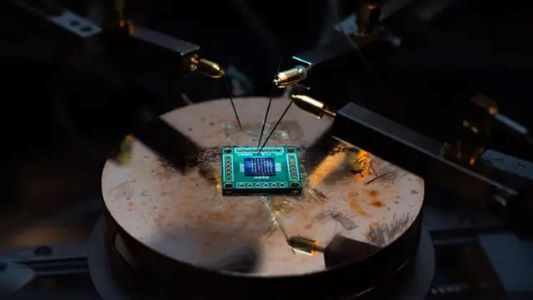

Scientists at KAUST (King Abdullah University of Science and Technology) (KAUST) have achieved a groundbreaking milestone – developing the world’s first six-layer hybrid CMOS chip.

This innovation signals a decisive shift in how the semiconductor industry approaches scaling, efficiency, and integration, aligning with global trends toward miniaturization, flexible electronics, and post-Moore’s Law architectures.

**Source: Interesting Engineering | Author: Rupendra Brahambhatt

hashtagSemiconductor hashtagTechInnovation hashtagSupplyChain hashtagLeadership hashtagAsiaPacific

- Researchers at KAUST (King Abdullah University of Science and Technology) (KAUST) have successfully built the first six-stack hybrid CMOS microchip, tripling previous integration limits and redefining possibilities in vertical chip design. It represents a fundamental shift toward 3D-structured architectures that expand performance without shrinking transistor size.

- The achievement addresses long-standing limits in traditional planar semiconductor scaling, where quantum interference and production costs have stalled miniaturization. Vertical stacking now emerges as the most promising alternative pathway for chip evolution.

- The hybrid CMOS combines organic and inorganic materials, enabling new levels of energy efficiency and signal integrity. The design balances flexibility with electrical precision, setting a new benchmark for next-generation electronics.

- The fabrication process introduced low-temperature manufacturing — below 150°C — to avoid damaging lower layers. This approach allows multiple layers to be built sequentially while maintaining alignment and structural stability.

- Each layer contains unique transistor materials that complement each other’s electrical properties, maximizing performance. Careful surface preparation and alignment were key to ensuring consistent signal flow between layers.

- The resulting chip demonstrated stable operation and energy-efficient logic circuits, confirming that vertical stacking can deliver higher performance without overheating or signal interference.

- The research suggests significant potential for flexible and wearable devices, from medical implants to smart textiles. Compact, bendable sensors may soon be designed using similar architectures.

- Applications could extend to the Internet of Things (IoT), space exploration, and environmental monitoring, where lightweight, power-efficient computing is critical for distributed or remote systems.

- For the semiconductor industry, this marks a potential paradigm shift beyond the constraints of Moore’s Law. The adoption of hybrid, multi-layer designs could reshape packaging technologies, supply chains, and equipment ecosystems over the coming decade.

- In terms of employment and skills in the Asia-Pacific, advances in hybrid chipmaking may accelerate demand for engineers skilled in low-temperature processing, materials integration, and advanced packaging – opening new roles in both R&D and production.

**Source: Interesting Engineering | Author: Rupendra Brahambhatt

Need Efficient Semiconductor Packaging Or Top Executive And Technical Talent?

We deliver high-quality carrier tapes, cover tapes, reels, and thermoforming trays tailored for the industry’s most in-demand and advanced packages — from PDIP, SOIC, and QFNs to WLCSP, chiplets, modules, and panels. At the same time, we connect you with the best-fit Senior Management leaders, Professionals, and Technical Staff to strengthen your organization. If this resonates, feel free to reach out — I personally check every message.

#Semiconductor #TechInnovation #SupplyChain #Leadership #AsiaPacific

Contact:

- For semiconductor packaging solutions (SG / APAC): https://bit.ly/3NdBhGB | chuck@superpak.com.sg

- For leadership, technical staff, & remote talent deployment: https://bit.ly/43myTXt | richard.olivas@tmbsconsulting.com

- For digital, social & content marketing strategy: richard@vector9.in

- WhatsApp Chuck Olivas: +65 8339 3490