IBM’s latest nanosheet transistor breakthrough slashes the power barrier and crams more capability into ever-smaller chips – accelerating the semiconductor evolution.

This leap comes at a pivotal moment as AI, quantum compute, and geopolitical supply chain dynamics demand faster, denser, and more energy-efficient silicon.

hashtagSemiconductor hashtagTechInnovation hashtagSupplyChain hashtagLeadership hashtagAsiaPacific

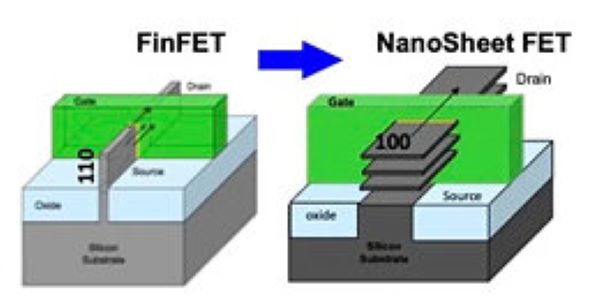

- IBM’s nanosheet architecture, also known as Gate-All-Around (GAA), pushes transistor scaling to the 2 nm node by stacking ultrathin “nanosheet” ribbons, enabling superior electrical control and density.

- The 2 nm test chip boasts up to 50 billion transistors on a fingernail-sized surface, marking a major milestone in Moore’s Law evolution.

- Compared to FinFET designs, GAA nanosheet technology delivers ~45% performance improvement or up to ~75% lower power consumption at equivalent speeds.

- The nickname “Ninja transistor” comes from its stealth-like ability to deliver high performance while dramatically reducing power leakage – allowing chips to run cooler and more efficiently without visible design compromises.

- IBM’s novel inner spacer design, paired with bottom dielectric isolation and EUV lithography, reduced gate lengths to ~12 nm – just a few dozen atoms thick—while ensuring precise control of electrical characteristics.

- This transistor variation enables multi-threshold-voltage (Multi-Vt) designs, giving engineers more flexibility to optimize different chip blocks for power or performance.

- While not yet in mass production, IBM’s 2 nm nanosheet roadmap aligns with upcoming enterprise AI, high-performance computing, and hybrid cloud products, ensuring commercial relevance.

- The architectural versatility of nanosheets – from adjustable sheet widths to custom logic configurations – makes it possible to fine-tune designs for specific workloads, including record-density SRAM (~38 Mb/mm²).

- Widespread adoption of nanosheet GAA transistors will drive multibillion-dollar investments in fabrication, design automation tools, and materials R&D – fueling broader semiconductor ecosystem growth.

- Asia-Pacific’s advanced fabs and engineering talent pipelines are well-positioned to capture significant market share in nanosheet manufacturing, boosting high-skill employment and regional tech leadership.

Looking for efficient semiconductor packaging solutions or top executive, professional, and technical talent? We’re your trusted partner for high-quality carrier tapes, cover tapes, and thermoforming trays – supporting all package types from WLCSP, BGA, QFP, SSOP, TSOP, and PDIP to advanced Fan-Out, 2.5D/3D IC, and Chiplet integration.

- Explore packaging solutions: https://bit.ly/3NdBhGB

- Find leadership and technical talent: https://bit.ly/43myTXt

- Contact us: chuck@superpak.com.sg | richard.olivas@tmbsconsulting.com

#semiconductormanufacturing #SemiconductorSolutions #ExecutiveSearch #TechnicalRecruitment #HiringProfessionals #SemiconductorGrowth